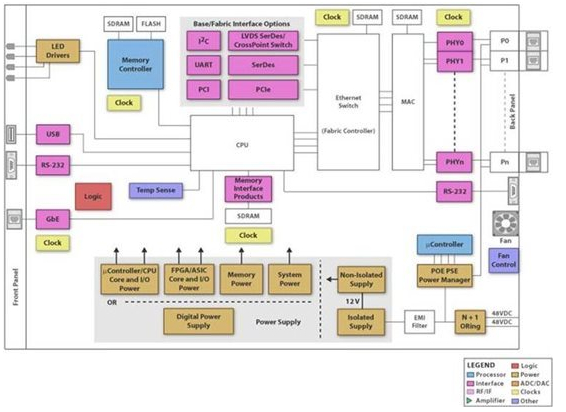

在设计系统时,时钟很可能是最后考虑的事情。如果不尽早考虑时钟方案,很可能会有所疏忽,除非您设计的是只需要一两个时钟信号的简单系统。例如,以太网交换机需要大量的系统级时钟频率。图 1 中的实例是包含 5 个时钟块的以太网交换机方框图。

图 1.具有大量时钟要求的以太网交换机方框图。

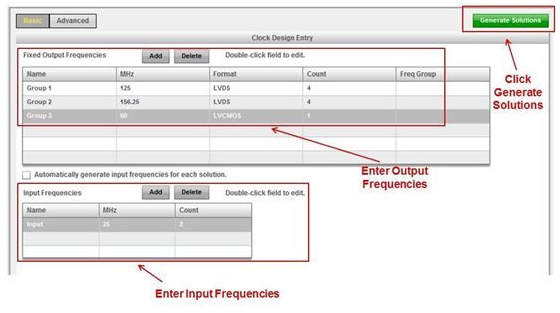

设计时钟系统的第一步是制定输入输出信号。在这个阶段,您将定义输入/输出频率、输出格式与端口数量。一旦找到了一系列可在应用中使用的时钟产品,就需要深入考虑数据完整性、低抖动与相位噪声等问题。

这里的时钟系统设计要求非常多,不过我们先来看一下特定应用需求。例如,您要为具有以下要求的以太网应用设计时钟系统:

输入频率

25 MHz

提供 2 个

输出频率

第 1 组

125 MHz

LVDS

4 个输出

第 2 组

156.25 MHz

LVDS

4 个输出

第 3 组

50 MHz

LVCMOS

1 个输出

能解决以上问题的集成电路系统确实存在,但对一般设计人员来说查找时间可能非常漫长。还有一种阅读产品说明书的方法是求助工具来帮忙完成繁重的查找任务。

德州仪器 (TI) 可以解决这些问题的工具是 WEBENCH® 时钟架构。该工具不仅可帮助您为时钟系统找到适当的器件,而且还有助于仿真系统性能。

第一个时钟架构屏幕(图 2)需要立刻描述系统的输入/输出要求。

图 2.时钟系统输入输出规范

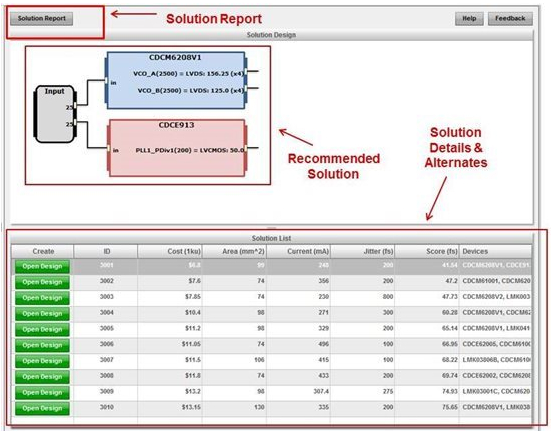

输入您的系统要求后,点击绿色“生成解决方案”按钮。就会出现针对您的问题而推荐的解决方案(图 3),以及解决方案下面表格中的几个其它选项。

图 3.时钟系统解决方案

看到不同电路选项后,您就可以查看您设计方案的解决方案报告。如果点击一个解决方案其它选项,推荐解决方案方框图就会改变。在本视图中,您可以查看解决方案报告。

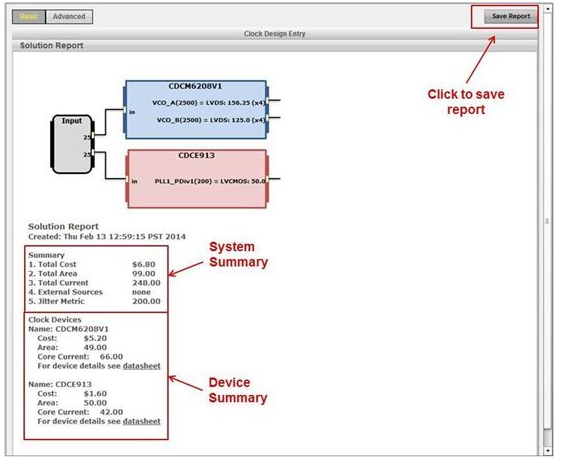

图 4.时钟系统设计总结

在解决方案报告中,您可看到系统总结,简单了解方框图的成本、面积及电流综合信息,以及每个器件的详细信息。本博客文章只为您提供该软件的简单介绍,但您可在该站点中发现更多潜在功能。试一试吧!点击 WEBENCH® 时钟架构,并告诉我们您的想法。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。